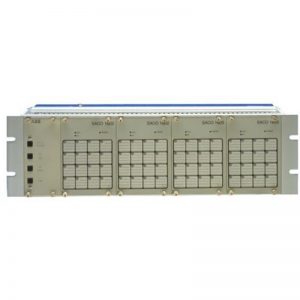

216DB61 HESG324063R100J | ABB| Dual redundant network cable connection

¥8,858.00

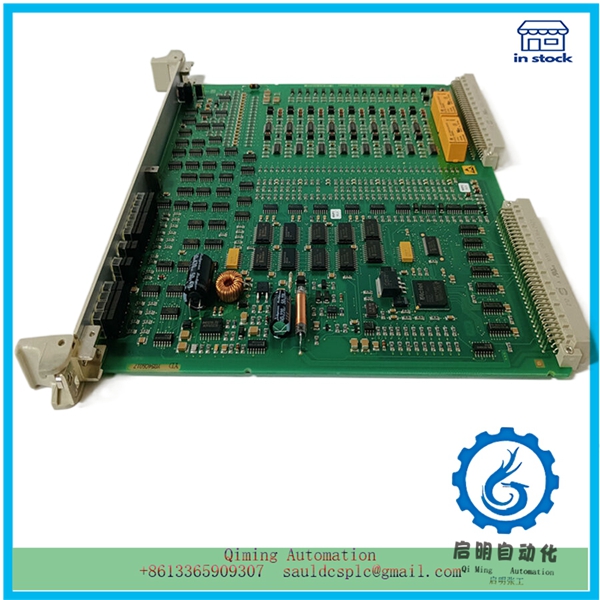

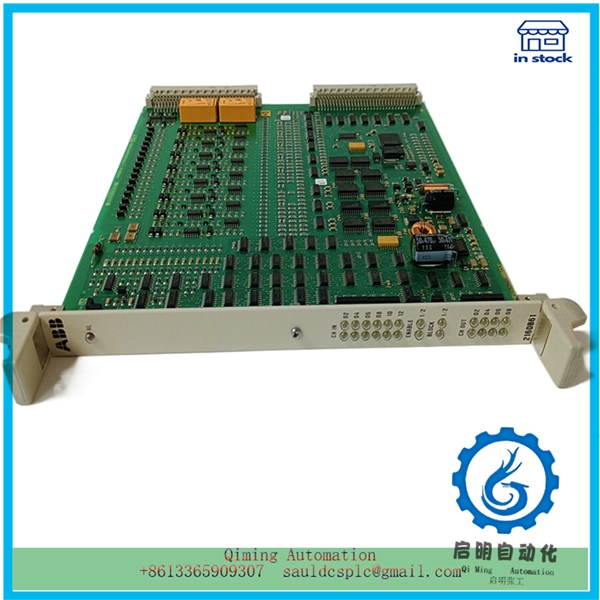

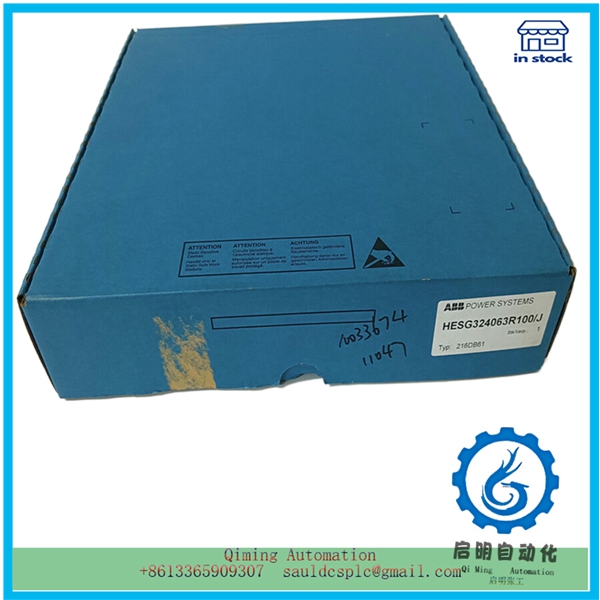

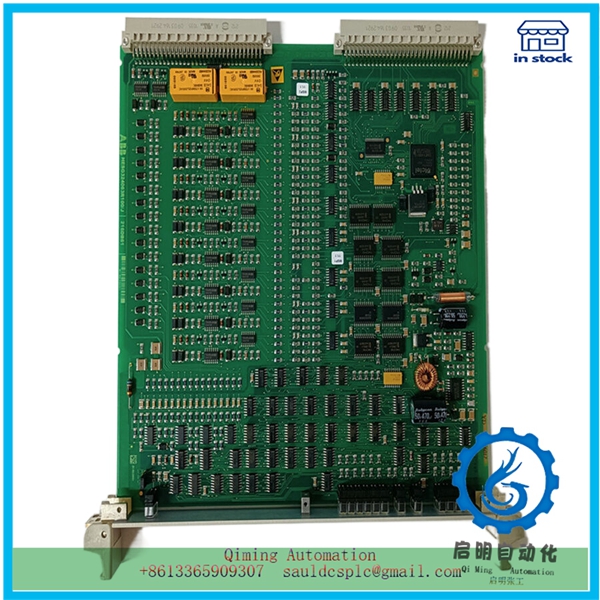

Module Number: 216DB61 HESG324063R100J

Product staus: Discontinued

Delivery time: In stock

Sales country: All over the world

Product situation: Brandnew , one year warranty

Product Size: 250*235*85mm

We may provide these service :Guidance manual /Datasheet/ Weight/ Size/ Orignal country/ Prodcuct COO & COM & COC

Certificate of conformity / Certificate of Origin / Certificate of Origin /Operation method

Delivery time/ Provide a one-year warranty / Brand New Original Authentic

Contact me: Sauldcsplc@gmail.com +8613822101417 SIMON

Have a good day! Thanks for watching my website!

Introduced Product:

COOPER GHG122

YOKOGAWA YS1700-100/A06/A31

AMAT 0190-27952

ABB UFC760BE1041 3BHE004573R1041

ABB USC329AE01 3BHB002483R0001

WATLOW ANAFAZE CLS204 204-C10000BL

Description

216DB61 HESG324063R100J | ABB| Dual redundant network cable connection

- .Many products are not yet on the shelves please contact us for more products

- .If there is any inconsistency between the product model and the picture on display, the model shall prevail. Contact us for the specific product picture, and we will arrange to take photos in the warehouse for confirmation

- .We have 16 shared warehouses around the world, so please understand that it can sometimes take several hours to accurately return to you. Of course, we will respond to your concerns as soon as possible

In the above 216DB61 HESG324063R100J , according to the requirements of Ethernet frame transfer process, interrupt handling at either end includes three different entities. Firstly, the interrupt response mechanism of the CPU core, followed by the processing of interrupt response with the requirements of the operating system, and then the PCIe hardware device also has a set of specifications for sending interrupts to the CPU operating system. The interrupt handling mechanism of either party can be described in lengthy text, which will not be further elaborated in this article.

The 216DB61 HESG324063R100J bus supports two interrupt modes, the traditional INTx interrupt and the interrupt request mechanism based on memory write requests, namely message interrupts. The design scheme in this article uses traditional INTx interrupts. For the convenience of description, we describe the interrupt processing flow from the perspective of FPGA timing diagram, which is specifically divided into the host (interrupt signal sent by PCIe to the host), PCIe hard core, interrupt enable signal configured by the driver, and interrupt source on the 216DB61 HESG324063R100J side. The following diagram shows the interrupt interaction process between the FPGA development board and the host when the host operating system is VxWorks.

Mailbox:sauldcsplc@gmail.com |216DB61 HESG324063R100J

www.abbgedcs.com | Qiming Industrial Automation| Simon +86 13822101417

Reviews

There are no reviews yet.