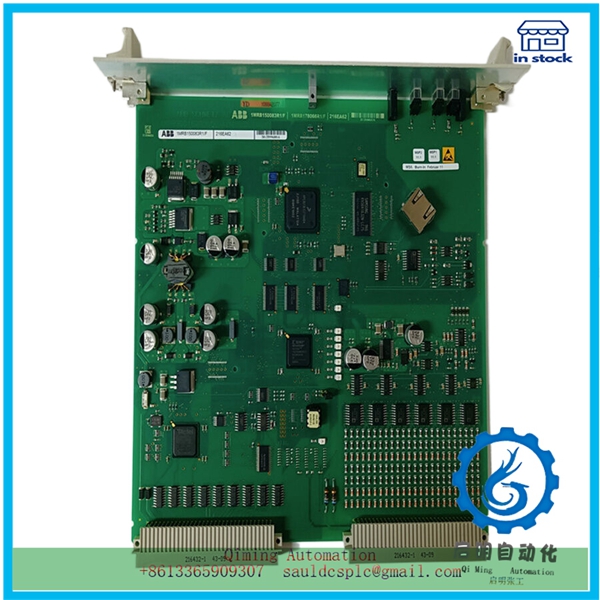

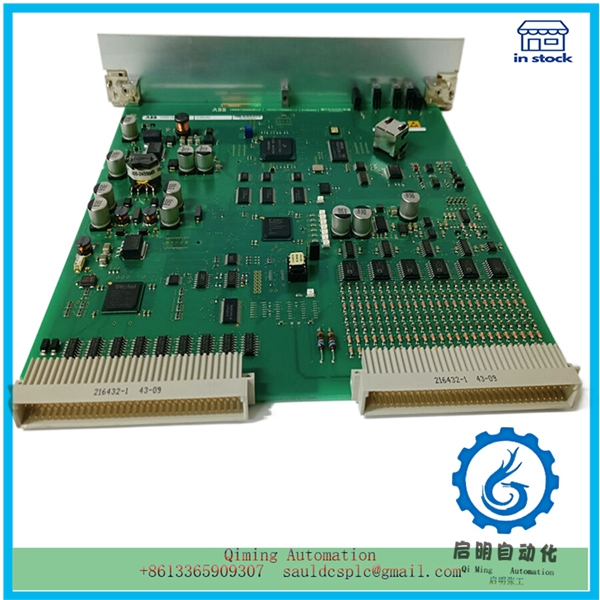

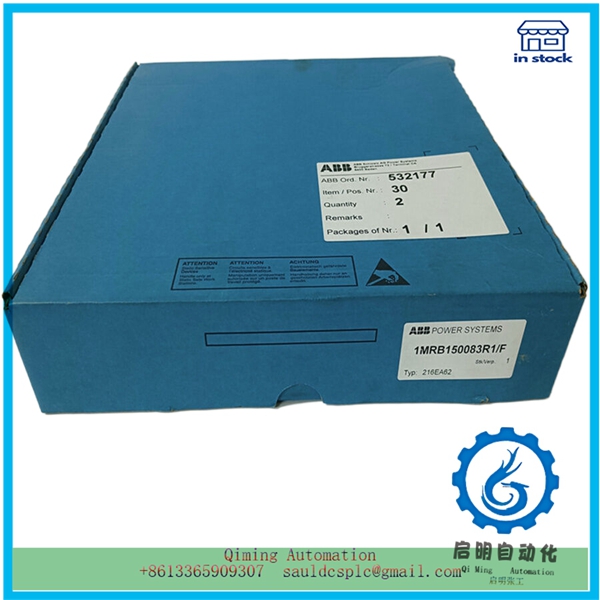

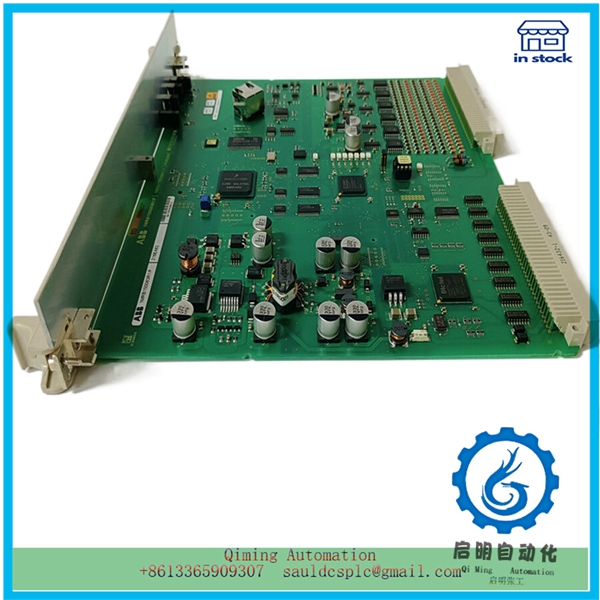

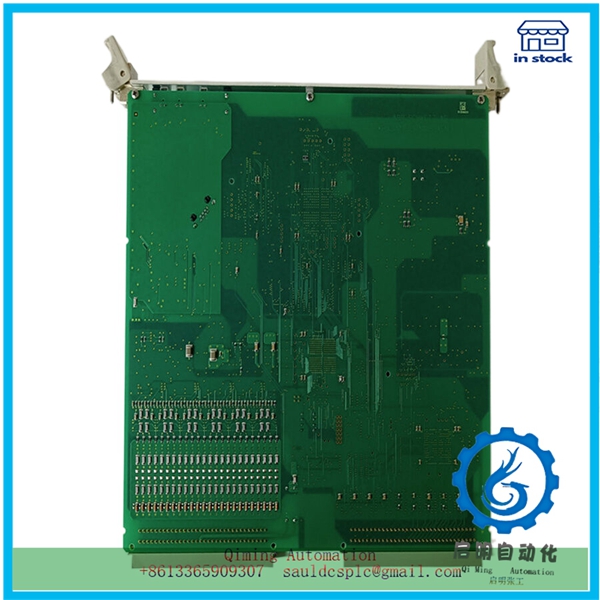

216EA62 1MRB150083R1F 1MRB178066R1F | ABB| PCIe IP Core Configuration MODULE

¥4,471.00

Module Number: 216EA62 1MRB150083R1F 1MRB178066R1F

Product staus: Discontinued

Delivery time: In stock

Sales country: All over the world

Product situation: Brandnew , one year warranty

Product Size: 250*235*85mm

We may provide these service :Guidance manual /Datasheet/ Weight/ Size/ Orignal country/ Prodcuct COO & COM & COC

Certificate of conformity / Certificate of Origin / Certificate of Origin /Operation method

Delivery time/ Provide a one-year warranty / Brand New Original Authentic

Contact me: Sauldcsplc@gmail.com +8613822101417 SIMON

Have a good day! Thanks for watching my website!

Introduced Product:

EATON F271-IS

GE P110-6052

ABB REM543BM215AAAB

METSO D201832L

ABB UUD148AE02

BENTLY 3500/22M 138607-01

BENTLY 3500/42M 128229-01

Bently 87199-01

Description

216EA62 1MRB150083R1F 1MRB178066R1F | ABB| PCIe IP Core Configuration MODULE

- .Many products are not yet on the shelves please contact us for more products

- .If there is any inconsistency between the product model and the picture on display, the model shall prevail. Contact us for the specific product picture, and we will arrange to take photos in the warehouse for confirmation

- .We have 16 shared warehouses around the world, so please understand that it can sometimes take several hours to accurately return to you. Of course, we will respond to your concerns as soon as possible

There are three interrupt sources on the 216EA62 1MRB150083R1F 1MRB178066R1F side that can trigger interrupts, namely DMA write start, DMA write completion, and DMA read completion interrupts. Among them, the write start interrupt source is when the FPGA informs the host that there is data to be uploaded through DMA write operations; The write completion interrupt is when the FPGA encapsulates all data into a DMA write request packet; The read completion interrupt is when the FPGA has received all DMA read completion packets from the host. The position “1” in the above figure indicates that the interrupt source mwr_start_interrupt has been raised.

If any interrupt source is raised, the 216EA62 1MRB150083R1F 1MRB178066R1F will configure the “set interrupt” timing for the PCIe IP core. After a successful handshake between cfg_interrupt and cfg_interrupt_rdy, if cfg_interrupt_1ssert is high, it is set as an interrupt. (cfg_interrupt is an interrupt request sent by the PCIe hard core to the host, and cfg_interrupt_rdy is the response received by the host after receiving the interrupt request. At this time, it is necessary to check the status of cfg_interrupt_1ssert. If it is high, it is set as an interrupt, as shown in “2” in the above figure; if it is low, it is clear as an interrupt request, as shown in “5” in the above figure.)

After a period of 216EA62 1MRB150083R1F 1MRB178066R1F (approximately 17 clocks in this case), the hard interrupt level INTA on the host side is raised, and it is only then that the FPGA board truly sends an interrupt to the host. As shown in “3” in the above figure.

Mailbox:sauldcsplc@gmail.com |216EA62 1MRB150083R1F 1MRB178066R1F

www.abbgedcs.com | Qiming Industrial Automation| Simon +86 13822101417

Reviews

There are no reviews yet.