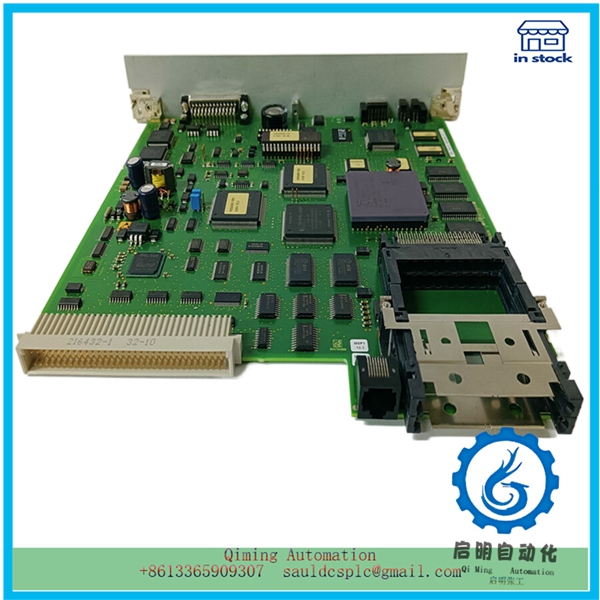

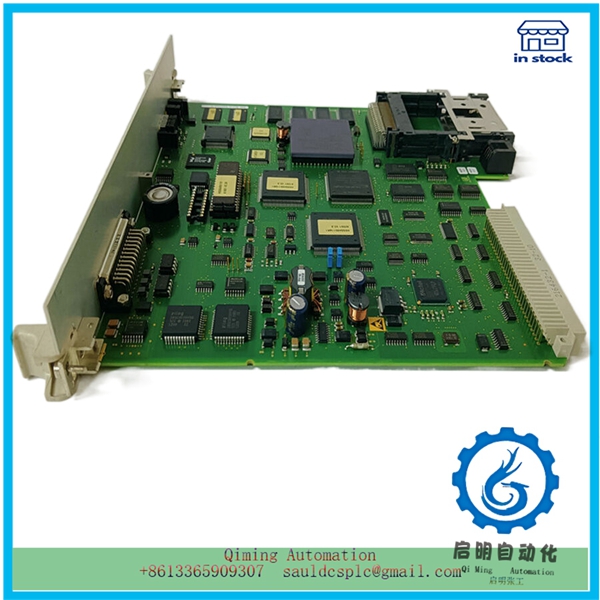

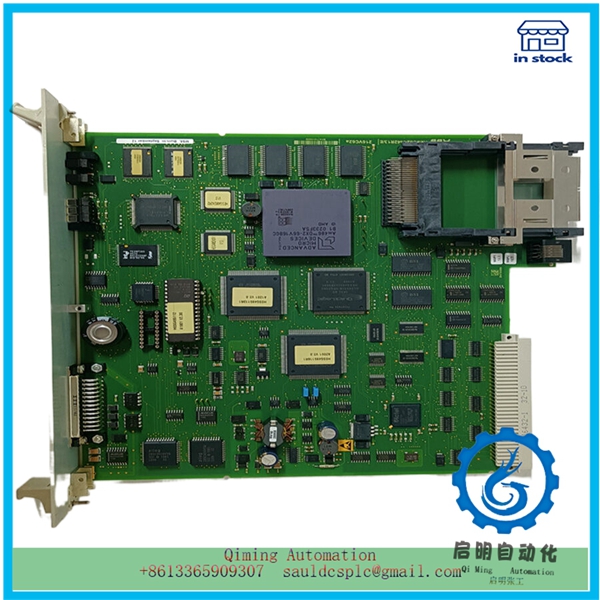

216VC62a HESG324442R13E HESG324442R112F| ABB| data transmission module

¥8,211.00

Module Number: 216VC62a HESG324442R13E HESG324442R112F

Product staus: Discontinued

Delivery time: In stock

Sales country: All over the world

Product situation: Brandnew , one year warranty

Product Size: 250*235*85mm

We may provide these service :Guidance manual /Datasheet/ Weight/ Size/ Orignal country/ Prodcuct COO & COM & COC

Certificate of conformity / Certificate of Origin / Certificate of Origin /Operation method

Delivery time/ Provide a one-year warranty / Brand New Original Authentic

Contact me: Sauldcsplc@gmail.com +8613822101417 SIMON

Have a good day! Thanks for watching my website!

Introduced Product:

BENTLY 3500/15 127610-01

BENTLY 3500/15 129489-01

BENTLY 3500/42M 176449-02

BENTLY 3500/32 125712-01

BENTLY 3500/92 136180-01

BENTLY 3500/15 125840-01

BENTLY 3500/15 129478-01

BENTLY 3500/32 125720-01

BENTLY 3500/92 133323-01

Description

216VC62a HESG324442R13E HESG324442R112F| ABB| data transmission module

- .Many products are not yet on the shelves please contact us for more products

- .If there is any inconsistency between the product model and the picture on display, the model shall prevail. Contact us for the specific product picture, and we will arrange to take photos in the warehouse for confirmation

- .We have 16 shared warehouses around the world, so please understand that it can sometimes take several hours to accurately return to you. Of course, we will respond to your concerns as soon as possible

In order to obtain the minimum interval for 216VC62a HESG324442R13E HESG324442R112F to respond to PCIe interrupts, we performed clock counting on the FPGA side for two “set interrupt” intervals, namely steps 2) and 10) in the figure above. Under the “set interrupt” timing (cfg_interupt_rdy&cfg_interupt_ssert), we reset the interval time register inter-intr_clk_cnt [31:0] count. Otherwise, the count is increased by one until the next “set interrupt” is reset, which can calculate the time interval for the interrupt signal to be raised twice.

During the testing process, we used Vivado to capture two different interrupt scenarios during actual data transmission.

With the 216VC62a HESG324442R13E HESG324442R112F of the interrupt handling process above, it is very convenient to analyze the waveform diagram under specific working conditions. From the above figure, it can be seen that the read completion interrupt mrd_one_interrupt triggers the interrupt setting timing. The hard interrupt level of the host is raised, and the driver writes “1” to the highest bit of the control and status register 04H (int_dis_o signal shown in the figure) PIO operation to turn off the interrupt function. At this time, the hardware no longer generates the interrupt setting timing until the driver jumps out of the interrupt reset program and writes “0” to the int_dis_o of 04H to enable the interrupt; The driver PIO reads the interrupt status register (indicated by the blue line) and samples it until the two interrupt flags, read complete (indicated by the mrd_dond_interrupt signal) and write start (indicated by the mwr_start_interrupt signal), are set to high. At this time, the 216VC62a HESG324442R13E HESG324442R112F records and simultaneously resets these two interrupt flags, and then executes the read complete interrupt and write start interrupt state machines respectively.

Mailbox:sauldcsplc@gmail.com |216VC62a HESG324442R13E HESG324442R112F

www.abbgedcs.com | Qiming Industrial Automation| Simon +86 13822101417

Reviews

There are no reviews yet.