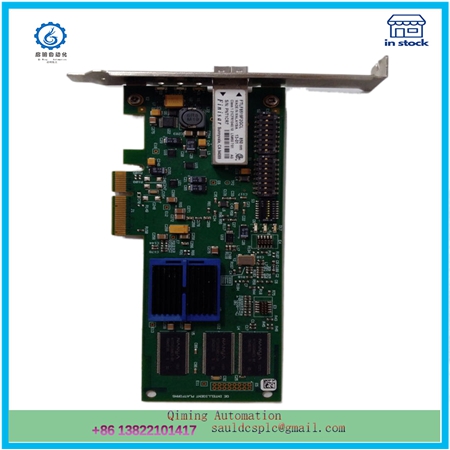

PCIE-5565-PIORC PCIE-5565PIORC-100000 350-9367875565-100000 A1

¥5,456.00

🔔Module Number: PCIE-5565-PIORC PCIE-5565PIORC-100000 350-9367875565-100000 A1

⚠️Product status: Discontinued

🏚️Delivery time: In stock

🆕Product status: 100% new

🌍Sales country: All over the world

🥇Product situation: one year warranty

📮Contact me: Sauldcsplc@gmail.com

💬Wechat/Whatsapp :+86 13822101417

☀️Have a good day! Thanks for watching my website!

Description

PCIE-5565-PIORC PCIE-5565PIORC-100000 350-9367875565-100000 A1

- .Many products are not yet on the shelves please contact us for more products

- .If there is any inconsistency between the product model and the picture on display, the model shall prevail. Contact us for the specific product picture, and we will arrange to take photos in the warehouse for confirmation

- .We have 16 shared warehouses around the world, so please understand that it can sometimes take several hours to accurately return to you. Of course, we will respond to your concerns as soon as possible

Of course, the connection between the power layer and the IC power pin must be as short as possible, as the rising edge of the digital signal becomes faster. It is best to directly connect to the solder pad where the IC power pin is located, which needs to be discussed separately.

In order to control common mode EMI, PCIE-5565-PIORC PCIE-5565PIORC-100000 350-9367875565-100000 A1 the power layer must facilitate decoupling and have a sufficiently low inductance. This power layer must be a well-designed pair of power layers. Someone may ask, to what extent is good enough to be considered good? The answer to the question depends on the layering of the power supply, the materials between layers, and the operating frequency (i.e., the function of IC rise time). Usually, the spacing between power layers is 6mil, and the interlayer is made of FR4 material, so the equivalent capacitance of each square inch of power layer is about 75pF. Obviously, the smaller the interlayer spacing, the larger the capacitance.

There are PCIE-5565-PIORC PCIE-5565PIORC-100000 350-9367875565-100000 A1 not many devices with a rise time of 100 to 300ps, but according to the current development speed of ICs, devices with a rise time in the range of 100 to 300ps will occupy a high proportion. For circuits with a rise time of 100 to 300ps, a 3mil layer spacing will no longer be suitable for most applications. At that time, it was necessary to adopt a layering technique with a interlayer spacing of less than 1mil and replace the FR4 dielectric material with a material with a high dielectric constant. Nowadays, ceramics and ceramic plastics can meet the design requirements of a 100 to 300ps rise time circuit.

-

Please contact us for the best price. Email: 【sauldcsplc@gmail.com】

-

For more products, click here

Mailbox:sauldcsplc@gmail.com | PCIE-5565-PIORC PCIE-5565PIORC-100000 350-9367875565-100000 A1

www.abbgedcs.com | Qiming Industrial Control | Simon +86 13822101417

Reviews

There are no reviews yet.