XDD501A101 3BHE036342R0101 | ABB | High level state module

¥8,754.00

Module Number: XDD501A101 3BHE036342R0101

Product status: Discontinued

Delivery time: In stock

Sales country: All over the world

Product situation: Brandnew , one year warranty

Contact me: Sauldcsplc@gmail.com +8613822101417 SIMON

Have a good day! Thanks for watching my website!

Introduced Product:

DKC01.3-200-7-FW

3HAC029818-001 DSQC663

IC698CPE040-FJ

PM511V16

PFEA113-20 3BSE050092R20

216VC62A HESG324442R13/E HESG324442R112/F

LDGRB-01 3BSE013177R1

KUC755AE105

AL81G

VMIVME7740-841

Description

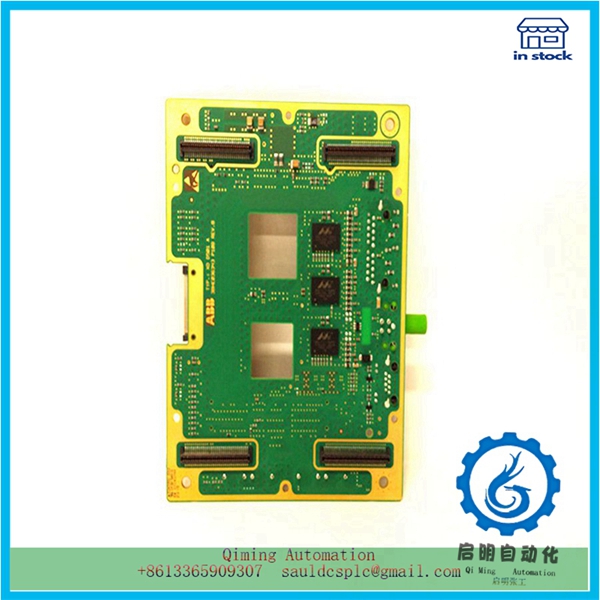

XDD501A101 3BHE036342R0101 | ABB | High level state module

- .Many products are not yet on the shelves please contact us for more products

- .If there is any inconsistency between the product model and the picture on display, the model shall prevail. Contact us for the specific product picture, and we will arrange to take photos in the warehouse for confirmation

- .We have 16 shared warehouses around the world, so please understand that it can sometimes take several hours to accurately return to you. Of course, we will respond to your concerns as soon as possible

XDD501A101 requires a master device responsible for initiating requests and controlling the clock; Other devices are slave devices that identify and respond to master device requests through device ID addresses. The master and slave devices need to take turns controlling SDA. At first, I didn’t understand this point, so I added I2C data code and measured it using an oscilloscope at the SDA and SCL pins. However, I could only find some messy waveforms without the expected effect. Later, the slave device was connected, and the code was written on both sides, responding to each other. Only then did the waveform be seen on the oscilloscope.

From the graph, it can be seen that the timing is as follows:

Initiated by the host, when XDD501A101 is at high level, SDA undergoes high to low shear, forming a start signal;

Next are the 7-bit address and a read-write flag. Here, the 7-bit address is 0111100, which is 0x3c, which is the address ID set in our code; The last digit of 0 indicates a write operation;

Next, at the next clock, the master releases the SDA in a high-level state, and the slave responds by pulling the SDA down;

Next are two 8-bit data XDD501A101 and the response, which is 0x2E, which is the ASCII code with the “.” symbol and matches the expected output;

There are other data and the last stop bit, which have been truncated in the figure.

Mailbox:sauldcsplc@gmail.com |XDD501A101 3BHE036342R0101

www.abbgedcs.com | Qiming Industrial Control | Simon +86 13822101417

We may provide the information of this product:

Guidance manual PDF /Datasheet/ Weight/ Size/ Orignal country/ Prodcuct COO & COM & COC

Certificate of conformity / Certificate of Origin / Certificate of Origin /Operation method

Delivery time/ Provide a one-year warranty / Brand New Original Authentic

Reviews

There are no reviews yet.